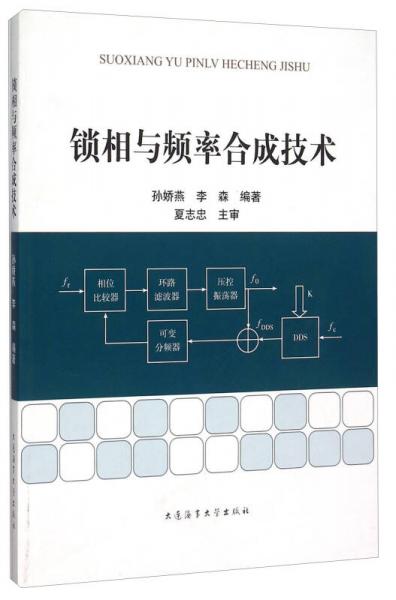

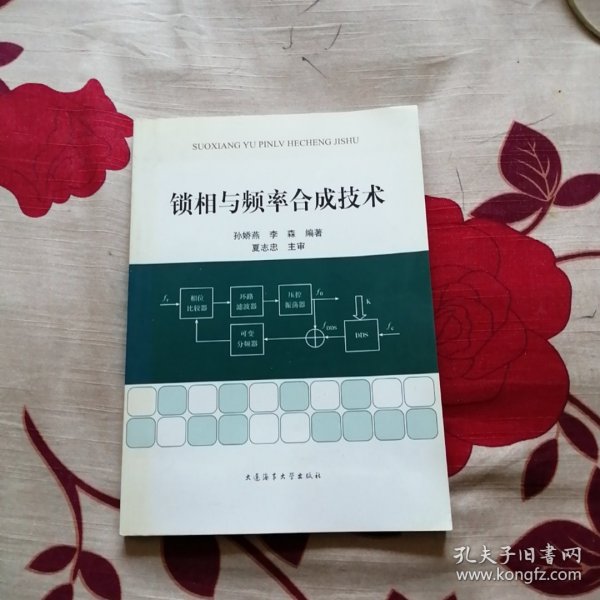

锁相与频率合成技术

出版时间:

2009-05

版次:

1

ISBN:

9787563223084

定价:

27.00

装帧:

平装

开本:

16开

纸张:

胶版纸

页数:

250页

字数:

402千字

正文语种:

简体中文

3人买过

-

《锁相与频率合成技术》的内容分为三大部分。第一部分(第1~4章)重点介绍了锁相环路的工作原理;讨论了锁相环路的跟踪性能、捕获性能、稳定性能及噪声滤除能力:简要介绍了锁相环路在通信与电子系统中的应用。第二部分(第5~7章)在介绍频率合成基本单元电路的基础之上,重点讨论各种频率合成方法,其中包括:吞脉冲小数分频合成、∑一△调制小数分频合成、直接数字频率合成(DDS)术及DDS+PLL混合频率合成等各种频率合成方案。第三部分(第8—10章)重点介绍了集成化、全数字化、软件化的锁相与频率合成的实现方法。其中包括典型集成锁相环和集成频率合成器芯片及应用方法;阐述了全数字锁相环、软件锁相环的实现方法。

《锁相与频率合成技术》的特点是理论与实际应用结合,给出了大量应用实例;内容新,反映了本领域的研究与发展水平。

《锁相与频率合成技术》可用于高等学校通信工程专业的本科教材,也可作为通信工程技术人员和相关专业研究生学习参考。 第1章 概述

1.1 锁相与频率合成的基本概念

1.2 频率合成的方式和特点

1.3 锁相与频率合成技术的发展

第2章 锁相环路的工作原理

2.1 环路的基本工作原理

2.1.1 锁相的基本概念

2.1.2 锁相环的构成

2.1.3 环路的工作过程

2.2 锁相环路的相位模型

2.2.1 鉴相器的相位模型

2.2.2 压控振荡器的相位模型

2.2.3 环路滤波器模型

2.2.4 环路的相位模型与动态方程

2.3 锁相环路的传递函数

2.3.1 环路方程的线性化

2.3.2 线性环路的传递函数

第3章 锁相环路的性能

3.1 锁相环路的线性跟踪性能

3.1.1 环路的频率响应

3.1.2 环路对典型输入相位的跟踪性能

3.2 锁相环路的稳定性

3.2.1 环路稳定性判据

3.2.2 常用二阶环的稳定性

3.3 锁相环路的捕获特性

3.3.1 环路捕获的性能指标与分析方法

3.3.2 一阶环的捕获过程

3.3.3 二阶环的捕获过程

3.3.4 辅助捕捉方法

3.4 锁相环路的噪声性能分析

3.4.1 输入加性噪声的环路相位模型

3.4.2 环路对加性噪声的线性过滤性能

3.4.3 存在输入噪声环路的非线性性能

第4章 锁相环路的应用

4.1 在调制解调技术中的应用

4.1.1 锁相调制器

4.1.2 调频调相解调器

4.1.3 同步检波器

4.1.4 抑制载波的相干解调器

4.2 在载波提取与位同步技术中的应用

4.2.1 相干载波提取锁相环

4.2.2 位同步锁相环

4.3 在测速与测距技术中的应用

4.3.1 锁相接收机

4.3.2 跟踪测距锁相环

第5章 频率合成的方案

5.1 频漂抵消合成法

5.2 脉冲取样锁相环

5.3 数字单环频率合成器

5.3.1 单环合成器的相位模型

5.3.2 单环合成器的杂散干扰

5.3.3 单环合成器的噪声分析

5.3.4 混频环

5.4 多环数字频率合成器

5.4.1 双环数字频率合成器

5.4.2 三环数字频率合成器

第6章 锁相频率合成器的基本电路

6.1 鉴相器

6.1.1 二极管平衡鉴相器

6.1.2 取样保持鉴相器

6.1.3 开关型鉴相器

6.1.4 鉴频鉴相器

6.2 压控振荡器

6.2.1 压控振荡器的主要技术指标

6.2.1 LC压控振荡器

6.2.2 晶体压控振荡器

6.3 可变分频器

6.3.1 可变分频器的主要技术指标

6.3.2 可变分频器的工作原理

6.3.3 提高可变分频器速度的方法

6.3.4 减法可变分频器

6.3.5 吞脉冲技术

第7章 小数分频频率合成器

7.1 小数分频合成器的工作原理

7.1.1 小数分频器的实现方法

7.1.2 双模分频器控制信号的产生

7.1.3 小数分频环中鉴相器的输出电压

7.2 改善输出频谱纯度

7.2.1 可变延迟法

7.2.2 模拟相位补偿法

7.2.3 数控补偿法

7.2.4 ∑一△调制技术

7.3 小数分频器的实用电路

7.3.1 基本小数分频器

7.3.2 吞脉冲小数分频器

7.4 小数分频频率合成器方案实例

第8章 直接数字频率合成器

8.1 直接数字频率合成器工作原理

8.1.1 斜升波合成

8.1.2 任意波形的合成

8.1 _3正弦波合成

8.2 DDS的频谱特性分析

8.2.1 DDS的技术特性

8.2.2 理想情况下DDS输出频谱特性

8.2.3 DDS中杂散信号频谱特性分析

8.3 DDS与PLL混合频率合成方案

8.3.1 DDS驱动PLL混合方案

8.3.2 DDS插入PLL混合方案

8.3.3 DDS用作小数分频器

8.4 DDS在电子系统中的应用

8.4.1 DDS在数据通信中的应用

8.4 -2 DDS在雷达系统中的应用

8.4.3 DDS在电子测量仪器中的应用

8.5 DDS典型芯片介绍

8.5.1 DDS芯片AD9854

8.5.2 DDS芯片Q2368

8.5.3 DDS芯片STEL-1180

第9章 集成频率合成器

9.1 集成锁相环基本电路

9.1.1 集成鉴相器

9.1.2 集成压控振荡器

9.1.3 集成双模分频器及其他电路

9.2 单片集成锁相环

9.2.1 低频数字锁相环CD4046

9.2.2 高频单片模拟锁相环L562

9.3 集成频率合成器

9.3.1 并行码输入方式的频率合成器

9.3.2 数据总线输入方式的频率合成器

9.3.3 串行输入方式的频率合成器

9.4 集成频率合成器的微机控制

9.4.1 串行码输入方式频率合成器的微机控制

9.4.2 数据总线输入方式频率合成器的微机控制

9.4.3 并行码输入方式频率合成器的微机控制

第10章 全数字锁相环

10.1 全数字型鉴相器

10.1.1 由触发器和计数器构成的全数字型鉴相器

10.1.2 奈奎斯特率全数字型鉴相器

10.1.3 零交叉全数字型鉴相器

10.2 全数字环路滤波器

10.2.1 超前/滞后计数器式全数字环路滤波器

10.2.2 K变模计数器式全数字环路滤波器

10.2.3 N先于M式全数字环路滤波器

10.3 数字控制振荡器

10.3.1 除Ⅳ可变分频器式DCO

10.3.2 增量-减量计数器式DCO

10.3.3 波形合成器式DCO

10.4 全数字锁相环方案

10.4.1 超前/滞后型全数字锁相环

10.4.2 触发器型全数字锁相环

10.4.3 全数字锁相环实例

10.5 全数字锁相环的性能

10.5.1 全数字锁相环的离散时间工作特性

10.5.2 全数字锁相环输出频率的变化范围

10.5.3 全数字锁相环的频域分析

10.5.4 全数字锁相环的纹波消除技术

10.6 软件锁相环

10.6.1 模拟锁相环的软件实现

10.6.2 数模混合锁相环的软件实现

10.6.3 全数字锁相环的软件实现

参考文献

-

内容简介:

《锁相与频率合成技术》的内容分为三大部分。第一部分(第1~4章)重点介绍了锁相环路的工作原理;讨论了锁相环路的跟踪性能、捕获性能、稳定性能及噪声滤除能力:简要介绍了锁相环路在通信与电子系统中的应用。第二部分(第5~7章)在介绍频率合成基本单元电路的基础之上,重点讨论各种频率合成方法,其中包括:吞脉冲小数分频合成、∑一△调制小数分频合成、直接数字频率合成(DDS)术及DDS+PLL混合频率合成等各种频率合成方案。第三部分(第8—10章)重点介绍了集成化、全数字化、软件化的锁相与频率合成的实现方法。其中包括典型集成锁相环和集成频率合成器芯片及应用方法;阐述了全数字锁相环、软件锁相环的实现方法。

《锁相与频率合成技术》的特点是理论与实际应用结合,给出了大量应用实例;内容新,反映了本领域的研究与发展水平。

《锁相与频率合成技术》可用于高等学校通信工程专业的本科教材,也可作为通信工程技术人员和相关专业研究生学习参考。

-

目录:

第1章 概述

1.1 锁相与频率合成的基本概念

1.2 频率合成的方式和特点

1.3 锁相与频率合成技术的发展

第2章 锁相环路的工作原理

2.1 环路的基本工作原理

2.1.1 锁相的基本概念

2.1.2 锁相环的构成

2.1.3 环路的工作过程

2.2 锁相环路的相位模型

2.2.1 鉴相器的相位模型

2.2.2 压控振荡器的相位模型

2.2.3 环路滤波器模型

2.2.4 环路的相位模型与动态方程

2.3 锁相环路的传递函数

2.3.1 环路方程的线性化

2.3.2 线性环路的传递函数

第3章 锁相环路的性能

3.1 锁相环路的线性跟踪性能

3.1.1 环路的频率响应

3.1.2 环路对典型输入相位的跟踪性能

3.2 锁相环路的稳定性

3.2.1 环路稳定性判据

3.2.2 常用二阶环的稳定性

3.3 锁相环路的捕获特性

3.3.1 环路捕获的性能指标与分析方法

3.3.2 一阶环的捕获过程

3.3.3 二阶环的捕获过程

3.3.4 辅助捕捉方法

3.4 锁相环路的噪声性能分析

3.4.1 输入加性噪声的环路相位模型

3.4.2 环路对加性噪声的线性过滤性能

3.4.3 存在输入噪声环路的非线性性能

第4章 锁相环路的应用

4.1 在调制解调技术中的应用

4.1.1 锁相调制器

4.1.2 调频调相解调器

4.1.3 同步检波器

4.1.4 抑制载波的相干解调器

4.2 在载波提取与位同步技术中的应用

4.2.1 相干载波提取锁相环

4.2.2 位同步锁相环

4.3 在测速与测距技术中的应用

4.3.1 锁相接收机

4.3.2 跟踪测距锁相环

第5章 频率合成的方案

5.1 频漂抵消合成法

5.2 脉冲取样锁相环

5.3 数字单环频率合成器

5.3.1 单环合成器的相位模型

5.3.2 单环合成器的杂散干扰

5.3.3 单环合成器的噪声分析

5.3.4 混频环

5.4 多环数字频率合成器

5.4.1 双环数字频率合成器

5.4.2 三环数字频率合成器

第6章 锁相频率合成器的基本电路

6.1 鉴相器

6.1.1 二极管平衡鉴相器

6.1.2 取样保持鉴相器

6.1.3 开关型鉴相器

6.1.4 鉴频鉴相器

6.2 压控振荡器

6.2.1 压控振荡器的主要技术指标

6.2.1 LC压控振荡器

6.2.2 晶体压控振荡器

6.3 可变分频器

6.3.1 可变分频器的主要技术指标

6.3.2 可变分频器的工作原理

6.3.3 提高可变分频器速度的方法

6.3.4 减法可变分频器

6.3.5 吞脉冲技术

第7章 小数分频频率合成器

7.1 小数分频合成器的工作原理

7.1.1 小数分频器的实现方法

7.1.2 双模分频器控制信号的产生

7.1.3 小数分频环中鉴相器的输出电压

7.2 改善输出频谱纯度

7.2.1 可变延迟法

7.2.2 模拟相位补偿法

7.2.3 数控补偿法

7.2.4 ∑一△调制技术

7.3 小数分频器的实用电路

7.3.1 基本小数分频器

7.3.2 吞脉冲小数分频器

7.4 小数分频频率合成器方案实例

第8章 直接数字频率合成器

8.1 直接数字频率合成器工作原理

8.1.1 斜升波合成

8.1.2 任意波形的合成

8.1 _3正弦波合成

8.2 DDS的频谱特性分析

8.2.1 DDS的技术特性

8.2.2 理想情况下DDS输出频谱特性

8.2.3 DDS中杂散信号频谱特性分析

8.3 DDS与PLL混合频率合成方案

8.3.1 DDS驱动PLL混合方案

8.3.2 DDS插入PLL混合方案

8.3.3 DDS用作小数分频器

8.4 DDS在电子系统中的应用

8.4.1 DDS在数据通信中的应用

8.4 -2 DDS在雷达系统中的应用

8.4.3 DDS在电子测量仪器中的应用

8.5 DDS典型芯片介绍

8.5.1 DDS芯片AD9854

8.5.2 DDS芯片Q2368

8.5.3 DDS芯片STEL-1180

第9章 集成频率合成器

9.1 集成锁相环基本电路

9.1.1 集成鉴相器

9.1.2 集成压控振荡器

9.1.3 集成双模分频器及其他电路

9.2 单片集成锁相环

9.2.1 低频数字锁相环CD4046

9.2.2 高频单片模拟锁相环L562

9.3 集成频率合成器

9.3.1 并行码输入方式的频率合成器

9.3.2 数据总线输入方式的频率合成器

9.3.3 串行输入方式的频率合成器

9.4 集成频率合成器的微机控制

9.4.1 串行码输入方式频率合成器的微机控制

9.4.2 数据总线输入方式频率合成器的微机控制

9.4.3 并行码输入方式频率合成器的微机控制

第10章 全数字锁相环

10.1 全数字型鉴相器

10.1.1 由触发器和计数器构成的全数字型鉴相器

10.1.2 奈奎斯特率全数字型鉴相器

10.1.3 零交叉全数字型鉴相器

10.2 全数字环路滤波器

10.2.1 超前/滞后计数器式全数字环路滤波器

10.2.2 K变模计数器式全数字环路滤波器

10.2.3 N先于M式全数字环路滤波器

10.3 数字控制振荡器

10.3.1 除Ⅳ可变分频器式DCO

10.3.2 增量-减量计数器式DCO

10.3.3 波形合成器式DCO

10.4 全数字锁相环方案

10.4.1 超前/滞后型全数字锁相环

10.4.2 触发器型全数字锁相环

10.4.3 全数字锁相环实例

10.5 全数字锁相环的性能

10.5.1 全数字锁相环的离散时间工作特性

10.5.2 全数字锁相环输出频率的变化范围

10.5.3 全数字锁相环的频域分析

10.5.4 全数字锁相环的纹波消除技术

10.6 软件锁相环

10.6.1 模拟锁相环的软件实现

10.6.2 数模混合锁相环的软件实现

10.6.3 全数字锁相环的软件实现

参考文献

查看详情

-

全新

河北省保定市

平均发货22小时

成功完成率80.32%

-

全新

河北省保定市

平均发货26小时

成功完成率92.4%

-

全新

河北省保定市

平均发货9小时

成功完成率90.24%

-

全新

河北省保定市

平均发货27小时

成功完成率80.49%

-

全新

河北省保定市

平均发货18小时

成功完成率87.29%

-

全新

河北省保定市

平均发货25小时

成功完成率89.31%

-

锁相与频率合成技术

部分图书软件采集的图片与文字介绍不符,请以文字描述为准,自动忽略图片。

全新

河北省保定市

平均发货39小时

成功完成率82.15%

-

全新

河北省保定市

平均发货26小时

成功完成率87.82%

-

全新

河北省保定市

平均发货26小时

成功完成率87.82%

-

全新

河北省保定市

平均发货28小时

成功完成率86.4%

-

全新

北京市房山区

平均发货29小时

成功完成率83.8%

-

全新

河北省保定市

平均发货42小时

成功完成率84.25%

-

全新

河北省保定市

平均发货25小时

成功完成率84.54%

-

全新

河北省保定市

平均发货24小时

成功完成率92.32%

-

全新

河北省保定市

平均发货24小时

成功完成率92.32%

-

全新

山东省泰安市

平均发货24小时

成功完成率82.35%

-

全新

北京市丰台区

平均发货44小时

成功完成率84.1%

-

全新

河北省保定市

平均发货25小时

成功完成率89.44%

-

锁相与频率合成技术

本店所售图书,保证正版新书,有个别图片和实书封面不一样,以实书封面为准,有需要确定的可以联系客服。我店不能开发票。当天下单第二天发货。

全新

-

全新

河北省保定市

平均发货37小时

成功完成率86.77%

-

锁相与频率合成技术

书名,书号为准,图片自动采集偶尔有可能不一致,书名单本图片是套装,书名为准,无赠品

九五品

河北省保定市

平均发货13小时

成功完成率85.13%

-

全新

北京市房山区

平均发货32小时

成功完成率81.21%

-

全新

北京市丰台区

平均发货44小时

成功完成率84.1%

-

全新

北京市丰台区

平均发货44小时

成功完成率84.1%

-

九五品

辽宁省大连市

平均发货12小时

成功完成率93.58%

-

全新

河北省保定市

平均发货43小时

成功完成率67.83%

-

九五品

河北省保定市

平均发货16小时

成功完成率83.33%

-

全新

河北省保定市

平均发货21小时

成功完成率85.05%

-

全新

福建省漳州市

平均发货11小时

成功完成率94.7%

-

全新

江苏省南京市

平均发货22小时

成功完成率69.54%

-

锁相与频率合成技术

正版现货,品相完好,套书默认发一本,若是多种封面版本的书,请咨询客服再下单,有批发需求的联系客服

九品

北京市海淀区

平均发货18小时

成功完成率94.2%

-

全新

河北省保定市

平均发货27小时

成功完成率65.93%

-

全新

河北省保定市

平均发货31小时

成功完成率74.67%

-

全新

河北省保定市

平均发货15小时

成功完成率87.4%

-

全新

河北省保定市

平均发货33小时

成功完成率61.29%

-

全新

北京市房山区

平均发货11小时

成功完成率16.67%

占位居中

占位居中