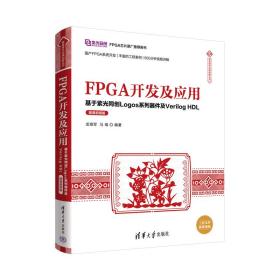

FPGA开发及应用——基于紫光同创Logos系列器件及VerilogHDL(微课视频版)(信息

出版时间:

2022-10

版次:

1

ISBN:

9787302610373

装帧:

平装

开本:

16开

纸张:

胶版纸

页数:

360页

字数:

509.000千字

5人买过

-

《FPGA开发及应用――基于紫光同创Logos系列器件及Verilog HDL(微课视频版)》以紫光同创公司的FPGA为例,全面系统地讲述了基于可编程逻辑器件的设计方法,结合实践讲解了大量的典型实例,便于读者理解和演练。书中从国内企业生产的EDA工具的使用到FPGA应用设计,再到Cortex-M1软核处理器的设计与应用,几乎涉及FPGA开发设计的所有知识,具体内容包括紫光同创FPGA芯片介绍、Pango Design Suite开发工具概述、Verilog语言、基本逻辑电路设计、ModelSim仿真、IP介绍、大量实例讲解、Cortex-M1设计开发等。

《FPGA开发及应用――基于紫光同创Logos系列器件及Verilog HDL(微课视频版)》可作为FPGA开发初学者及工程技术人员的参考用书,也可作为电子信息工程、计算机科学与技术等相关专业本科生、研究生的教材。

目录

第1章FPGA芯片及板卡介绍

1.1FPGA技术发展及基本架构

1.1.1FPGA的发展

1.1.2FPGA内部结构

1.2国内FPGA技术发展情况

1.3紫光同创FPGA芯片介绍

1.3.1Logos系列FPGA概述

1.3.2Logos系列FPGA产品特性

1.3.3Logos系列FPGA资源规模与封装信息

1.3.4Logos系列FPGA模块介绍

1.3.5Logos系列FPGA参考资料

1.4ALINX FPGA板卡介绍

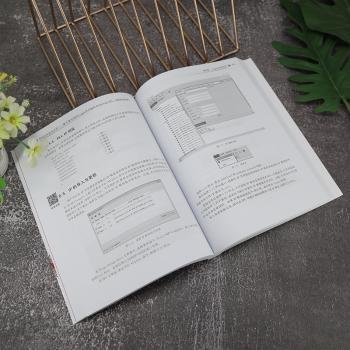

第2章Pango Design Suite开发环境

2.1安装Pango Design Suite软件

2.1.1安装步骤

2.1.2License关联

2.2PDS工程

2.2.1创建工程

2.2.2Verilog代码编写

2.2.3添加UCE约束

2.2.4生成位流文件

2.3菜单栏介绍

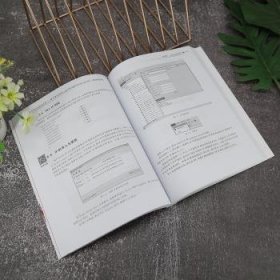

2.4User Constraint Editor简介

2.4.1UCE启动

2.4.2UCE主界面功能

2.4.3Timing Constraints界面

2.4.4Attribute表格界面

2.4.5Device界面

2.5ADS综合工具简介

2.5.1ADS Flow概述

2.5.2ADS综合的基本操作

2.5.3ADS综合网表分析

2.6PDS软件中的IP调用

2.6.1启动IPC

2.6.2主控窗口

2.6.3参数配置窗口

2.7在线分析仪的使用

2.7.1下载电缆

2.7.2Debugger连接

2.7.3Fabric Debugger说明

2.8PDS软件技巧与经验总结

2.8.1Synthesize 参数设置

2.8.2PNR参数设置

2.8.3常见报错分析与处理方法

第3章Verilog HDL 语法

3.1Verilog简介

3.2数据类型

3.2.1常量

3.2.2变量

3.3运算符

3.3.1算术运算符

3.3.2赋值运算符

3.3.3关系运算符

3.3.4逻辑运算符

3.3.5条件运算符

3.3.6位运算符

3.3.7移位运算符

3.3.8拼接运算符

3.3.9优先级

3.4组合逻辑

3.4.1与门

3.4.2或门

3.4.3非门

3.4.4异或

3.4.5比较器

3.4.6半加器

3.4.7全加器

3.4.8乘法器

3.4.9数据选择器

3.4.1038译码器

3.4.11三态门

3.5时序逻辑

3.5.1D触发器

3.5.2两级D触发器

3.5.3带异步复位D触发器

3.5.4带异步复位同步清零D触发器

3.5.5移位寄存器

3.5.6单口RAM

3.5.7伪双口RAM

3.5.8真双口RAM

3.5.9单口ROM

3.5.10有限状态机

3.6总结

第4章Verilog HDL数字电路设计

4.1基于格雷码编码器的设计

4.1.1简介

4.1.2实验原理

4.1.3程序代码

4.1.4验证结果

4.2异步清零加法器设计

4.2.1简介

4.2.2实验原理

4.2.3程序代码

4.2.4验证结果

4.3七段数码管显示电路的设计

4.3.1简介

4.3.2实验原理

4.3.3程序代码

4.3.4验证结果

4.4四位并行乘法器的设计

4.4.1简介

4.4.2实验原理

4.4.3程序代码

4.4.4验证结果

4.5基本触发器的设计

4.5.1简介

4.5.2实验原理

4.5.3程序代码

4.5.4验证结果

4.6四位全加器设计

4.6.1简介

4.6.2实验原理

4.6.3程序代码

4.6.4验证结果

4.7表决器的设计

4.7.1简介

4.7.2实验原理

4.7.3程序代码

4.7.4验证结果

4.8抢答器的设计

4.8.1简介

4.8.2实验原理

4.8.3程序代码

4.8.4验证结果

4.9序列检测器的设计

4.9.1简介

4.9.2实验原理

4.9.3程序代码

4.9.4验证结果

4.10数字频率计的设计

4.10.1简介

4.10.2实验原理

4.10.3程序代码

4.10.4验证结果

4.11数字钟的设计

4.11.1简介

4.11.2实验原理

4.11.3程序代码

4.11.4验证结果

第5章Testbench及其仿真

5.1Testbench设计

5.1.1Testbench简介

5.1.2Testbench的搭建

5.2ModelSim 介绍及仿真

5.2.1ModelSim简介

5.2.2ModelSim仿真

5.3PDS与ModelSim联合仿真

第6章Logos的常用IP

6.1RAM说明

6.1.1RAM简介

6.1.2RAM IP介绍

6.1.3RAM I/O框图

6.1.4RAM I/O引脚说明

6.1.5RAM时序模型

6.1.6RAM IP配置

6.1.7RAM IP例化

6.2ROM说明

6.2.1ROM简介

6.2.2ROM IP介绍

6.2.3ROM I/O框图

6.2.4ROM I/O引脚说明

6.2.5ROM 时序模型

6.2.6ROM IP配置

6.2.7ROM IP例化

6.3FIFO说明

6.3.1FIFO简介

6.3.2FIFO IP介绍

6.3.3FIFO I/O框图

6.3.4FIFO I/O引脚说明

6.3.5FIFO 时序模型

6.3.6FIFO IP配置

6.3.7FIFO IP例化

6.4PLL锁相环

6.4.1PLL简介

6.4.2PLL IP介绍

6.4.3PLL I/O框图

6.4.4PLL I/O引脚说明

6.4.5PLL IP配置

6.4.6PLL IP例化

6.5IP的导入与更新

6.6DDR IP 介绍

6.6.1DDR IP简介

6.6.2DDR IP系统框图

6.6.3DDR I/O框图

6.6.4DDR I/O引脚说明

6.6.5DDR IP配置

6.6.6DDR IP例化

6.7HSST IP介绍

6.7.1HSST IP简介

6.7.2HSST I/O接口

第7章基础实验

7.1LED流水灯

7.1.1实验原理

7.1.2程序解读

7.1.3Flash程序固化

7.2按键消抖程序设计

7.2.1简介

7.2.2实验原理

7.2.3程序解读

7.3串口程序设计

7.3.1简介

7.3.2实验原理

7.3.3程序解读

7.4HDMI显示程序设计

7.4.1简介

7.4.2实验原理

7.4.3程序解读

7.5DDR3存储程序设计

7.5.1简介

7.5.2实验原理

7.5.3程序解读

第8章进阶实验

8.1摄像头采集显示设计

8.1.1简介

8.1.2实验原理

8.1.3程序解读

8.2数码相框显示设计

8.2.1简介

8.2.2实验原理

8.2.3程序解读

8.3模数采集设计

8.3.1简介

8.3.2实验原理

8.3.3程序解读

8.4千兆以太网通信设计

8.4.1简介

8.4.2实验原理

8.4.3程序解读

8.5HSST通信设计

8.5.1简介

8.5.2实验原理

8.5.3程序解读

第9章综合实验

9.1基于FPGA的逻辑分析仪设计

9.1.1简介

9.1.2实验原理

9.1.3程序解读

9.2摄像头采集传输显示系统设计

9.2.1简介

9.2.2实验原理

9.2.3程序解读

第10章基于Pango CortexM1软核的程序开发

10.1CortexM1软核简介

10.2Pango CortexM1软核设计

10.2.1简介

10.2.2功能描述

10.2.3接口列表

10.2.4接口时序

10.2.5参考设计

10.2.6参考设计文件目录

10.2.7参考设计仿真

10.2.8参考设计上板验证

10.3CortexM1应用工程设计

10.3.1简介

10.3.2工程模板

10.4Hello World

10.4.1简介

10.4.2实验原理

10.5LED流水灯实验

10.5.1简介

10.5.2实验原理

10.6用户中断实验

10.6.1简介

10.6.2实验原理

10.7SPI接口读写实验

10.7.1简介

10.7.2实验原理

10.8串口收发实验

10.8.1简介

10.8.2实验原理

10.9I2C实验

10.9.1简介

10.9.2实验原理

10.10综合实验

10.10.1简介

10.10.2实验原理

参考文献

微课视频清单

视频名称时长/min书中位置

1彩榧内容简介和开发板硬件介绍5前言

2PDS和Modelsim安装72.1节节首

3LED流水灯工程设计242.2节节首

4Verilog基础语法1173.1节节首

5Verilog基础语法2153.3节节首

6Verilog基础语法3253.4节节首

7哺窭茁氡嗦肫84.1节节首

8惨觳角辶慵臃ㄆ94.2节节首

9彩码管显示104.3节节首

10渤朔ㄆ94.4节节首

11不本触发器74.5节节首

12菜奈蝗加器104.6节节首

13脖砭銎74.7节节首

14睬来鹌94.8节节首

15残蛄屑觳馄94.9节节首

16彩字频率计174.10节节首

17彩字时钟144.11节节首

18RAM介绍196.1节节首

19ROM介绍136.2节节首

20FIFO介绍176.3节节首

21PLL介绍106.4节节首

22蔡砑IP116.5节节首

23舶醇消抖137.2节节首

24泊口通信167.3节节首

25HDMI显示287.4节节首

26DDR读写测试227.5节节首

27采阆裢凡杉显示188.1节节首

28彩码相框显示358.2节节首

29材J采集显示188.3节节首

30睬д滓蕴网通信468.4节节首

31猜呒分析仪设计239.1节节首

32踩砗私樯2310.2节节首

33灿τ霉こ檀唇2110.3节节首

续表

视频名称时长/min书中位置

34Hello World810.4节节首

35LED流水灯810.5节节首

36灿没е卸610.6节节首

37SPI读写实验810.7节节首

38泊口收发实验810.8节节首

39I2C实验1010.9节节首

40沧酆鲜笛1710.10节节首

-

内容简介:

《FPGA开发及应用――基于紫光同创Logos系列器件及Verilog HDL(微课视频版)》以紫光同创公司的FPGA为例,全面系统地讲述了基于可编程逻辑器件的设计方法,结合实践讲解了大量的典型实例,便于读者理解和演练。书中从国内企业生产的EDA工具的使用到FPGA应用设计,再到Cortex-M1软核处理器的设计与应用,几乎涉及FPGA开发设计的所有知识,具体内容包括紫光同创FPGA芯片介绍、Pango Design Suite开发工具概述、Verilog语言、基本逻辑电路设计、ModelSim仿真、IP介绍、大量实例讲解、Cortex-M1设计开发等。

《FPGA开发及应用――基于紫光同创Logos系列器件及Verilog HDL(微课视频版)》可作为FPGA开发初学者及工程技术人员的参考用书,也可作为电子信息工程、计算机科学与技术等相关专业本科生、研究生的教材。

-

目录:

目录

第1章FPGA芯片及板卡介绍

1.1FPGA技术发展及基本架构

1.1.1FPGA的发展

1.1.2FPGA内部结构

1.2国内FPGA技术发展情况

1.3紫光同创FPGA芯片介绍

1.3.1Logos系列FPGA概述

1.3.2Logos系列FPGA产品特性

1.3.3Logos系列FPGA资源规模与封装信息

1.3.4Logos系列FPGA模块介绍

1.3.5Logos系列FPGA参考资料

1.4ALINX FPGA板卡介绍

第2章Pango Design Suite开发环境

2.1安装Pango Design Suite软件

2.1.1安装步骤

2.1.2License关联

2.2PDS工程

2.2.1创建工程

2.2.2Verilog代码编写

2.2.3添加UCE约束

2.2.4生成位流文件

2.3菜单栏介绍

2.4User Constraint Editor简介

2.4.1UCE启动

2.4.2UCE主界面功能

2.4.3Timing Constraints界面

2.4.4Attribute表格界面

2.4.5Device界面

2.5ADS综合工具简介

2.5.1ADS Flow概述

2.5.2ADS综合的基本操作

2.5.3ADS综合网表分析

2.6PDS软件中的IP调用

2.6.1启动IPC

2.6.2主控窗口

2.6.3参数配置窗口

2.7在线分析仪的使用

2.7.1下载电缆

2.7.2Debugger连接

2.7.3Fabric Debugger说明

2.8PDS软件技巧与经验总结

2.8.1Synthesize 参数设置

2.8.2PNR参数设置

2.8.3常见报错分析与处理方法

第3章Verilog HDL 语法

3.1Verilog简介

3.2数据类型

3.2.1常量

3.2.2变量

3.3运算符

3.3.1算术运算符

3.3.2赋值运算符

3.3.3关系运算符

3.3.4逻辑运算符

3.3.5条件运算符

3.3.6位运算符

3.3.7移位运算符

3.3.8拼接运算符

3.3.9优先级

3.4组合逻辑

3.4.1与门

3.4.2或门

3.4.3非门

3.4.4异或

3.4.5比较器

3.4.6半加器

3.4.7全加器

3.4.8乘法器

3.4.9数据选择器

3.4.1038译码器

3.4.11三态门

3.5时序逻辑

3.5.1D触发器

3.5.2两级D触发器

3.5.3带异步复位D触发器

3.5.4带异步复位同步清零D触发器

3.5.5移位寄存器

3.5.6单口RAM

3.5.7伪双口RAM

3.5.8真双口RAM

3.5.9单口ROM

3.5.10有限状态机

3.6总结

第4章Verilog HDL数字电路设计

4.1基于格雷码编码器的设计

4.1.1简介

4.1.2实验原理

4.1.3程序代码

4.1.4验证结果

4.2异步清零加法器设计

4.2.1简介

4.2.2实验原理

4.2.3程序代码

4.2.4验证结果

4.3七段数码管显示电路的设计

4.3.1简介

4.3.2实验原理

4.3.3程序代码

4.3.4验证结果

4.4四位并行乘法器的设计

4.4.1简介

4.4.2实验原理

4.4.3程序代码

4.4.4验证结果

4.5基本触发器的设计

4.5.1简介

4.5.2实验原理

4.5.3程序代码

4.5.4验证结果

4.6四位全加器设计

4.6.1简介

4.6.2实验原理

4.6.3程序代码

4.6.4验证结果

4.7表决器的设计

4.7.1简介

4.7.2实验原理

4.7.3程序代码

4.7.4验证结果

4.8抢答器的设计

4.8.1简介

4.8.2实验原理

4.8.3程序代码

4.8.4验证结果

4.9序列检测器的设计

4.9.1简介

4.9.2实验原理

4.9.3程序代码

4.9.4验证结果

4.10数字频率计的设计

4.10.1简介

4.10.2实验原理

4.10.3程序代码

4.10.4验证结果

4.11数字钟的设计

4.11.1简介

4.11.2实验原理

4.11.3程序代码

4.11.4验证结果

第5章Testbench及其仿真

5.1Testbench设计

5.1.1Testbench简介

5.1.2Testbench的搭建

5.2ModelSim 介绍及仿真

5.2.1ModelSim简介

5.2.2ModelSim仿真

5.3PDS与ModelSim联合仿真

第6章Logos的常用IP

6.1RAM说明

6.1.1RAM简介

6.1.2RAM IP介绍

6.1.3RAM I/O框图

6.1.4RAM I/O引脚说明

6.1.5RAM时序模型

6.1.6RAM IP配置

6.1.7RAM IP例化

6.2ROM说明

6.2.1ROM简介

6.2.2ROM IP介绍

6.2.3ROM I/O框图

6.2.4ROM I/O引脚说明

6.2.5ROM 时序模型

6.2.6ROM IP配置

6.2.7ROM IP例化

6.3FIFO说明

6.3.1FIFO简介

6.3.2FIFO IP介绍

6.3.3FIFO I/O框图

6.3.4FIFO I/O引脚说明

6.3.5FIFO 时序模型

6.3.6FIFO IP配置

6.3.7FIFO IP例化

6.4PLL锁相环

6.4.1PLL简介

6.4.2PLL IP介绍

6.4.3PLL I/O框图

6.4.4PLL I/O引脚说明

6.4.5PLL IP配置

6.4.6PLL IP例化

6.5IP的导入与更新

6.6DDR IP 介绍

6.6.1DDR IP简介

6.6.2DDR IP系统框图

6.6.3DDR I/O框图

6.6.4DDR I/O引脚说明

6.6.5DDR IP配置

6.6.6DDR IP例化

6.7HSST IP介绍

6.7.1HSST IP简介

6.7.2HSST I/O接口

第7章基础实验

7.1LED流水灯

7.1.1实验原理

7.1.2程序解读

7.1.3Flash程序固化

7.2按键消抖程序设计

7.2.1简介

7.2.2实验原理

7.2.3程序解读

7.3串口程序设计

7.3.1简介

7.3.2实验原理

7.3.3程序解读

7.4HDMI显示程序设计

7.4.1简介

7.4.2实验原理

7.4.3程序解读

7.5DDR3存储程序设计

7.5.1简介

7.5.2实验原理

7.5.3程序解读

第8章进阶实验

8.1摄像头采集显示设计

8.1.1简介

8.1.2实验原理

8.1.3程序解读

8.2数码相框显示设计

8.2.1简介

8.2.2实验原理

8.2.3程序解读

8.3模数采集设计

8.3.1简介

8.3.2实验原理

8.3.3程序解读

8.4千兆以太网通信设计

8.4.1简介

8.4.2实验原理

8.4.3程序解读

8.5HSST通信设计

8.5.1简介

8.5.2实验原理

8.5.3程序解读

第9章综合实验

9.1基于FPGA的逻辑分析仪设计

9.1.1简介

9.1.2实验原理

9.1.3程序解读

9.2摄像头采集传输显示系统设计

9.2.1简介

9.2.2实验原理

9.2.3程序解读

第10章基于Pango CortexM1软核的程序开发

10.1CortexM1软核简介

10.2Pango CortexM1软核设计

10.2.1简介

10.2.2功能描述

10.2.3接口列表

10.2.4接口时序

10.2.5参考设计

10.2.6参考设计文件目录

10.2.7参考设计仿真

10.2.8参考设计上板验证

10.3CortexM1应用工程设计

10.3.1简介

10.3.2工程模板

10.4Hello World

10.4.1简介

10.4.2实验原理

10.5LED流水灯实验

10.5.1简介

10.5.2实验原理

10.6用户中断实验

10.6.1简介

10.6.2实验原理

10.7SPI接口读写实验

10.7.1简介

10.7.2实验原理

10.8串口收发实验

10.8.1简介

10.8.2实验原理

10.9I2C实验

10.9.1简介

10.9.2实验原理

10.10综合实验

10.10.1简介

10.10.2实验原理

参考文献

微课视频清单

视频名称时长/min书中位置

1彩榧内容简介和开发板硬件介绍5前言

2PDS和Modelsim安装72.1节节首

3LED流水灯工程设计242.2节节首

4Verilog基础语法1173.1节节首

5Verilog基础语法2153.3节节首

6Verilog基础语法3253.4节节首

7哺窭茁氡嗦肫84.1节节首

8惨觳角辶慵臃ㄆ94.2节节首

9彩码管显示104.3节节首

10渤朔ㄆ94.4节节首

11不本触发器74.5节节首

12菜奈蝗加器104.6节节首

13脖砭銎74.7节节首

14睬来鹌94.8节节首

15残蛄屑觳馄94.9节节首

16彩字频率计174.10节节首

17彩字时钟144.11节节首

18RAM介绍196.1节节首

19ROM介绍136.2节节首

20FIFO介绍176.3节节首

21PLL介绍106.4节节首

22蔡砑IP116.5节节首

23舶醇消抖137.2节节首

24泊口通信167.3节节首

25HDMI显示287.4节节首

26DDR读写测试227.5节节首

27采阆裢凡杉显示188.1节节首

28彩码相框显示358.2节节首

29材J采集显示188.3节节首

30睬д滓蕴网通信468.4节节首

31猜呒分析仪设计239.1节节首

32踩砗私樯2310.2节节首

33灿τ霉こ檀唇2110.3节节首

续表

视频名称时长/min书中位置

34Hello World810.4节节首

35LED流水灯810.5节节首

36灿没е卸610.6节节首

37SPI读写实验810.7节节首

38泊口收发实验810.8节节首

39I2C实验1010.9节节首

40沧酆鲜笛1710.10节节首

查看详情

-

全新

河北省保定市

平均发货24小时

成功完成率92.43%

-

全新

北京市朝阳区

平均发货16小时

成功完成率96.18%

-

全新

山东省济宁市

平均发货67小时

成功完成率81.23%

-

全新

江苏省南京市

平均发货8小时

成功完成率96.53%

-

全新

河北省保定市

平均发货17小时

成功完成率82.91%

-

全新

河北省保定市

平均发货21小时

成功完成率83.64%

-

全新

河北省保定市

平均发货26小时

成功完成率87.83%

-

全新

河北省保定市

平均发货18小时

成功完成率87.81%

-

全新

河北省廊坊市

平均发货22小时

成功完成率86.67%

-

全新

河北省保定市

平均发货17小时

成功完成率85.82%

-

全新

山东省泰安市

平均发货8小时

成功完成率93.26%

-

全新

-

全新

河北省保定市

平均发货18小时

成功完成率87.81%

-

全新

江苏省无锡市

平均发货10小时

成功完成率93.45%

-

全新

北京市丰台区

平均发货24小时

成功完成率88.34%

-

全新

河北省保定市

平均发货28小时

成功完成率91.02%

-

全新

北京市朝阳区

平均发货18小时

成功完成率94.89%

-

全新

河北省保定市

平均发货26小时

成功完成率92.68%

-

全新

天津市西青区

平均发货14小时

成功完成率90.24%

-

全新

山东省泰安市

平均发货24小时

成功完成率92.43%

-

全新

广东省广州市

平均发货24小时

成功完成率80.08%

-

全新

北京市丰台区

平均发货26小时

成功完成率82.35%

-

全新

北京市朝阳区

平均发货19小时

成功完成率75.6%

-

全新

河北省保定市

平均发货20小时

成功完成率87.27%

-

全新

广东省广州市

平均发货19小时

成功完成率86.43%

-

全新

北京市朝阳区

平均发货18小时

成功完成率94.89%

-

全新

河北省保定市

平均发货26小时

成功完成率89.67%

-

全新

河北省保定市

平均发货26小时

成功完成率89.67%

-

全新

河北省保定市

平均发货23小时

成功完成率90.07%

-

全新

河北省保定市

平均发货15小时

成功完成率81.93%

-

全新

江苏省苏州市

平均发货9小时

成功完成率95.51%

-

全新

河北省保定市

平均发货18小时

成功完成率87.81%

-

全新

江苏省南京市

平均发货15小时

成功完成率83.14%

-

全新

江苏省南京市

平均发货7小时

成功完成率98.08%

-

全新

河北省保定市

平均发货24小时

成功完成率84.68%

-

全新

北京市房山区

平均发货29小时

成功完成率83.76%

-

全新

河北省保定市

平均发货24小时

成功完成率92.43%

-

全新

四川省成都市

平均发货15小时

成功完成率80.47%

-

全新

河北省保定市

平均发货25小时

成功完成率89.01%

-

全新

北京市通州区

平均发货9小时

成功完成率89.32%

-

全新

四川省成都市

平均发货23小时

成功完成率91.12%

-

全新

四川省成都市

平均发货15小时

成功完成率90.79%

-

全新

北京市丰台区

平均发货8小时

成功完成率90.65%

-

全新

北京市通州区

平均发货11小时

成功完成率94.17%

-

全新

山东省泰安市

平均发货18小时

成功完成率92.98%

-

全新

上海市黄浦区

平均发货11小时

成功完成率94.36%

-

全新

河北省保定市

平均发货26小时

成功完成率87.83%

-

全新

北京市西城区

平均发货27小时

成功完成率90.6%

-

九五品

北京市朝阳区

平均发货29小时

成功完成率85.62%

-

全新

山东省泰安市

平均发货22小时

成功完成率86.14%

占位居中

占位居中